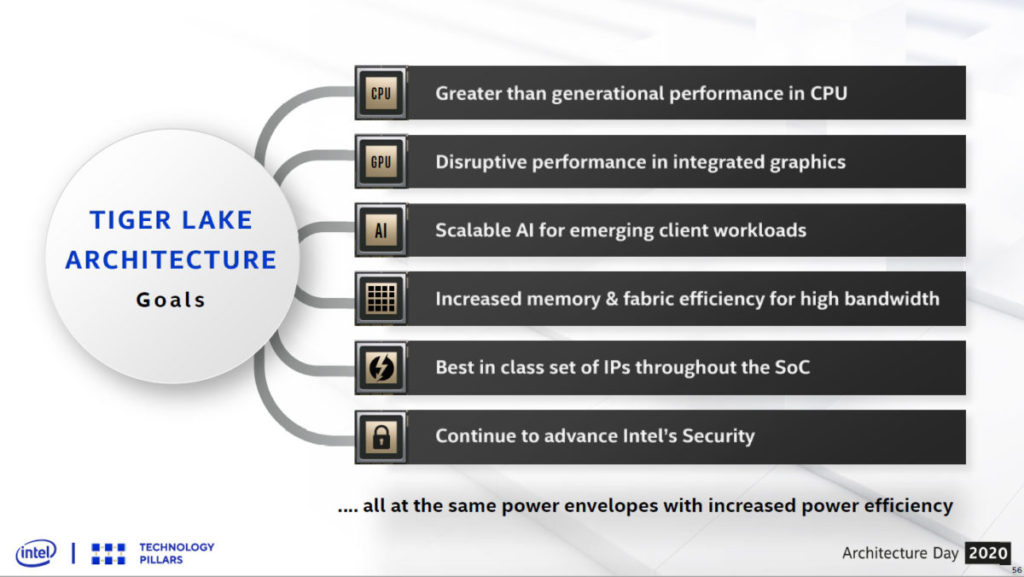

雖然 Intel 下一代筆電處理器 Tiger Lake 要 9 月 2 日才正式發表,但 AMD Ryzen 筆電來勢洶洶,Intel 也不敢怠慢。在 Intel Architecture Day 2020 率先公佈多項 Tiger Lake 微架構新技術,包括 10nm Super Fin 製程、全新 Willow Cove 微架構及 Xe-LP 繪圖引擎等,以達到比 AMD Zen2 快 25% IPC 性能的目標。

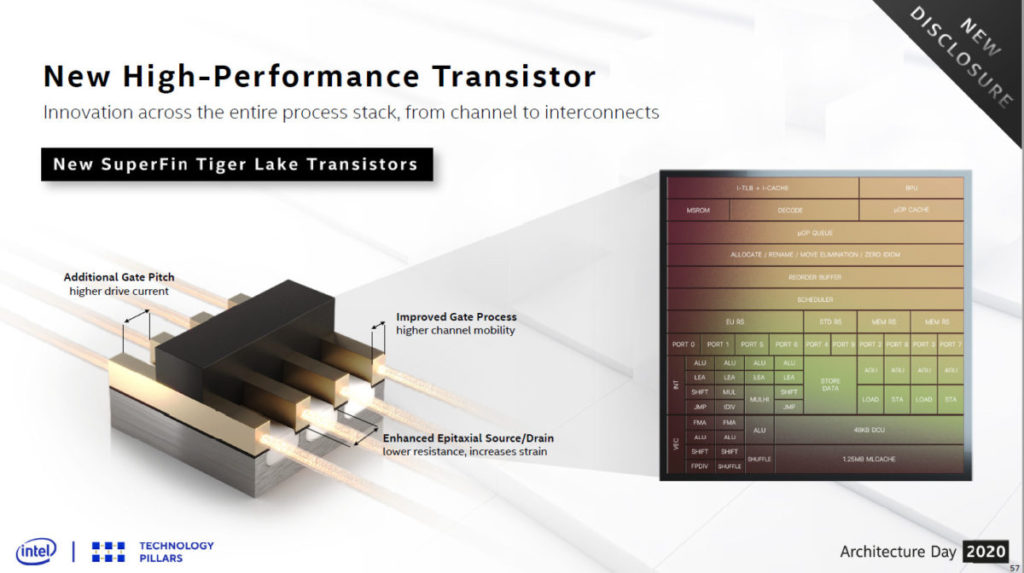

10nm SuperFin 製程有效提升時脈

針對上一代 Ice Lake 架構時脈偏低問題,最高的 Core i7-1068NG7 也僅有 4.1GHz 最大超頻時脈,丟人現眼,為此 Intel 在 Tiger Lake 上採用最新的10nm SuperFin 製程,也是 Intel 第 3 代 10nm 製程,可顯著提升時脈。

Intel 比較了 Ice Lake 及 Tiger Lake 兩代產品,後者不論是 Frequency Gains 及電力效能比均有明顯的改進,所以帶來更高的動態時脈,也就是所謂超頻時脈。

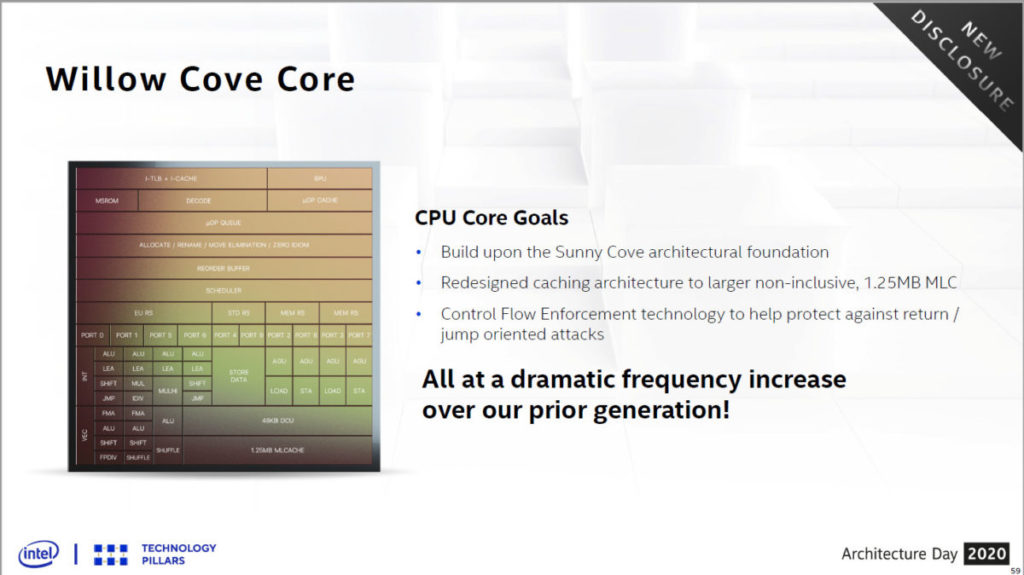

全新 Willow Cove 微架構

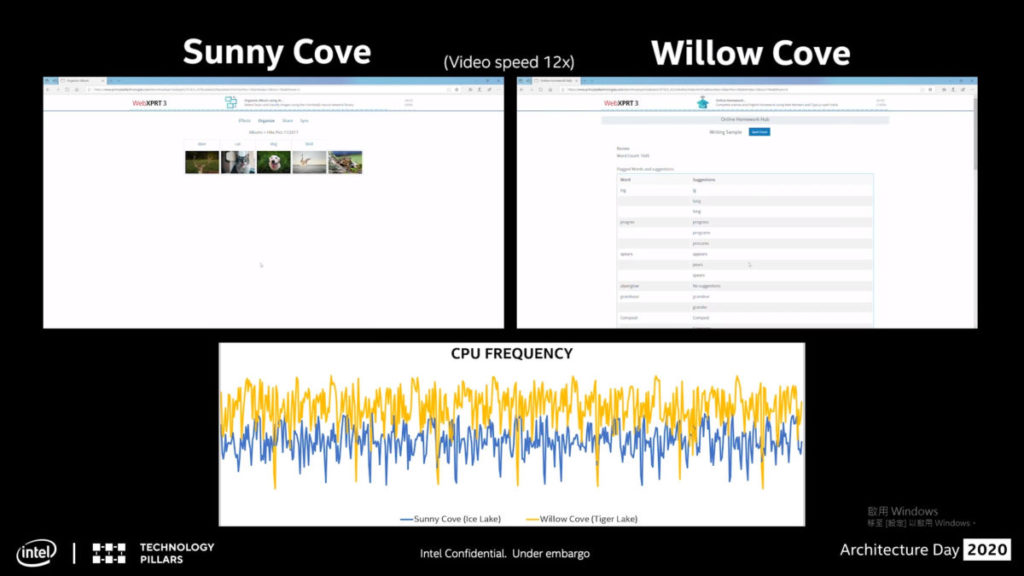

作為首款採用 Intel 的次世代 CPU 微架構 Willow Cove 之作,Tiger Lake 有先導性產品的作用,不容有失。Willow Cove 微架構保留現今 Sunny Cove 微架構的主要設計,如分支預測器 Brach Prediction Unit 及 10 個 Issue Port。Willow Cove 微架構所加強的,主要見在大幅度改善時脈表現和提升電力效率,以及重新設計的 Cache 架構。

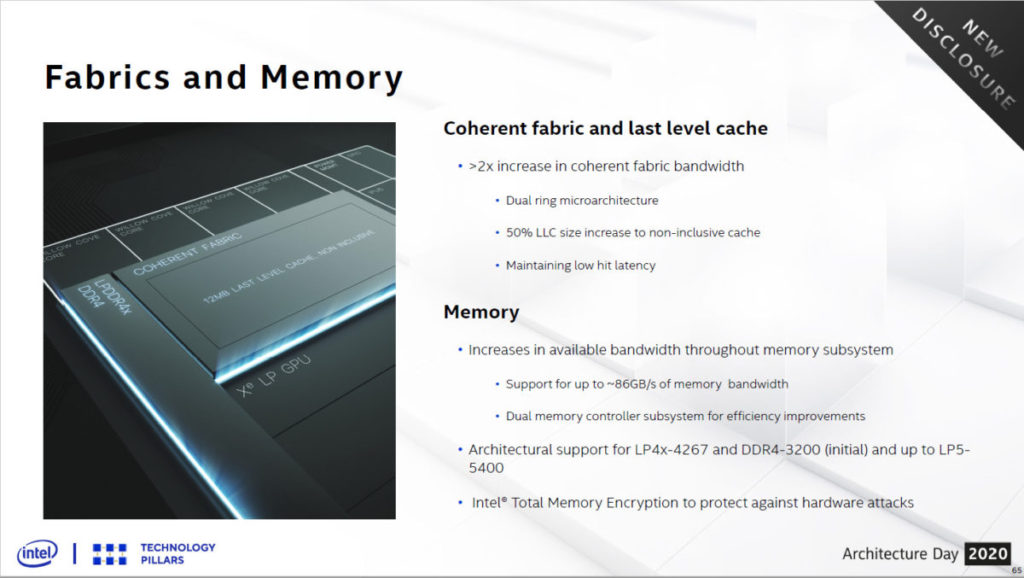

Willow Cove L2 Cache 容量達到 1.25MB MLC Cache ( Ice lake 為 512KB ),而且是屬於 Non-inclusive 架構,且有別於過去的 Inclusive 架構,使 L2 Cache 不用複製 L1 Data Cache 的內容而使可用 Cache 容量得到增加。與此同時,在 LCC ( 即 L3 Cache ) 連接的 Coherent fabric 頻寬也增加 1 倍、Cache 容量增加 50% 至 12MB ( Ice Lake 為 8MB ),同時維持 Low hit latency 以確保維持高效能。

支援 DDR5、PCI-E 4.0 及 TB4

在 Tiger Lake 架構,DDR4-3200 將是最低要求,新架構將可支援 LP4x-4267 記憶體,以及未來的 LP5-5400 即 DDR5 記憶體,開創新的時代。在 Ice Lake 上未能到支援的 PCI-E 4.0 將得到支持,而在 Ice Lake上 的 Thunderbolt 3 功能將進化至 Thunderbolt 4。考慮到目前主要的 Comet Lake ( 即 14nm ) 並未支援 Thunderbolt 3 功能,所以升級 Tiger Lake 將使 Thunderbolt 成為主流配置。另外,Tiger Lake 將採用 Intel 控制流強制技術 ( Intel Control-flow Enforcement Technology ),可防止 return/jump 等安全攻擊,增強安全性能。

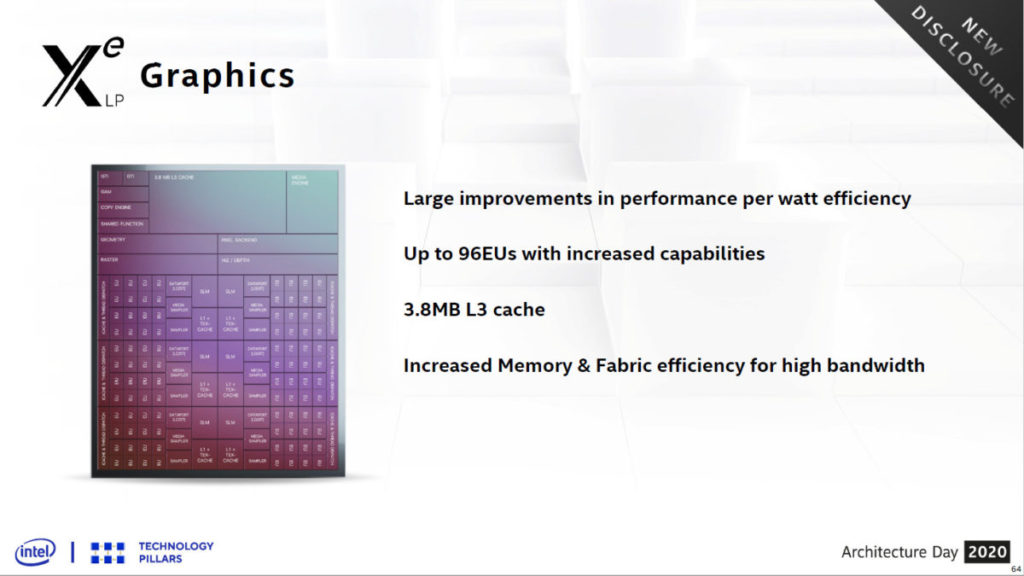

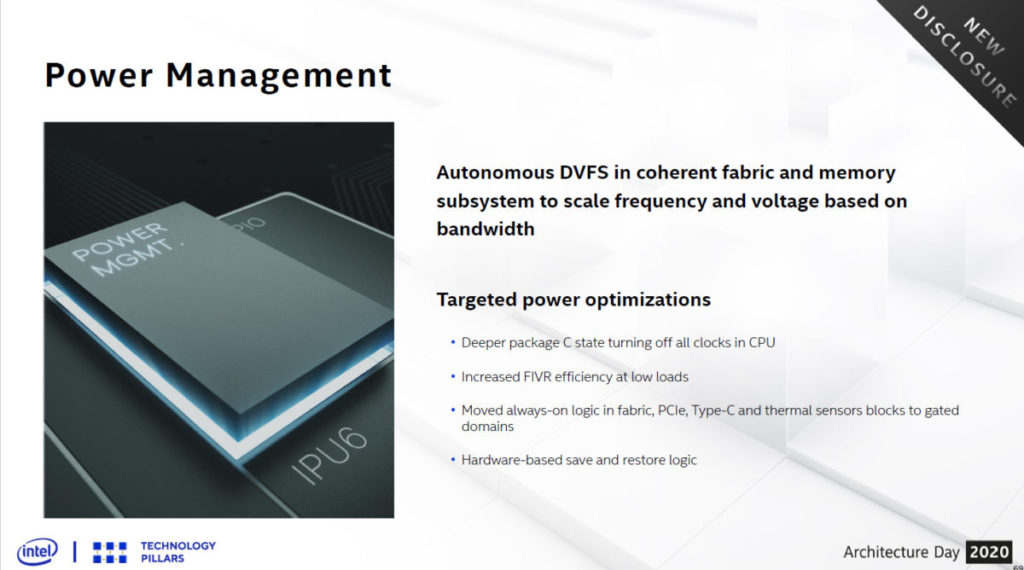

整合全新 Xe-LP 繪圖引擎

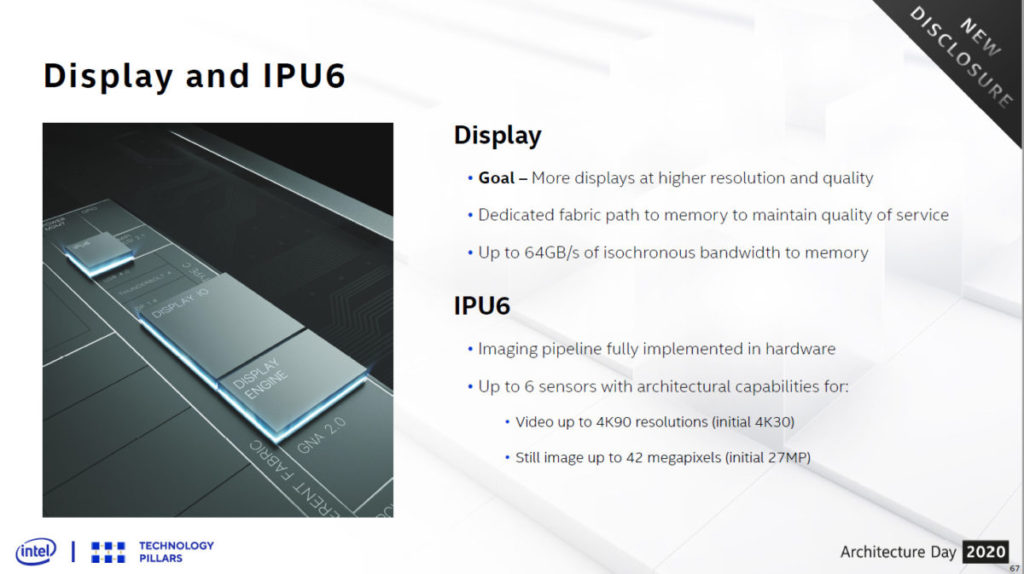

針對 Intel UHD Graphics 效能不濟的問題,Tiger Lake 將採用代號 Gen 12 的 Xe-LP 全新繪圖引擎,最多達提供 96 組 EU ,較 Ice Lake 的最多 64 組 EU 增加 50% 執行單元。在顯示輸出的 IPU6 功能方面,Tiger Lake 也作出加強,可支援最高 4K @90Hz,支援 4,200 萬像素影像等等。